-

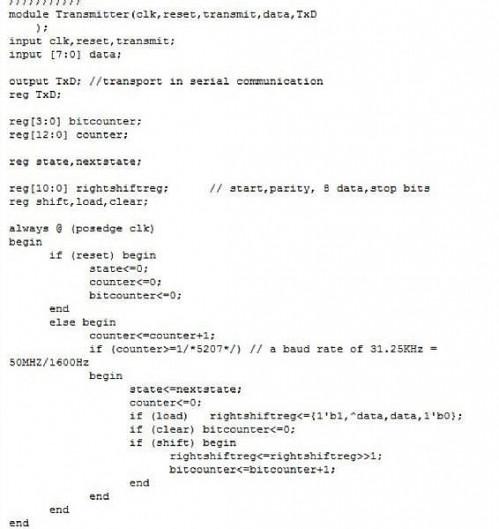

Cómo crear un simple transmisor UART serie en Verilog HDL

-

La mayor parte del transmisor receptor asíncrono universal (UART) que he encontrado en Internet, son demasiado complicados y difíciles de entender, aquí voy a explicar una teoría simple y también el código sobre la manera de construir una.Instrucciones

1 En primer lugar vamos a hablar acerca de cómo funcionan los transmisores. El principio básico es el envío de múltiples bits de datos a través de una sola línea. En nuestro transmisor, estos datos es paralelo, sin embargo para reducir el número de cables requeridos, utilizamos la comunicación en serie que se convierte en paralelo en el extremo receptor.

Las cosas básicas que necesitamos son los siguientes:

Un divisor de reloj (nuestro contador)

Esto nos permite es para enviar datos a una cierta velocidad (velocidad de transmisión). Nuestro receptor tomará muestras y tomar el bit de datos a poco.Un registro de desplazamiento

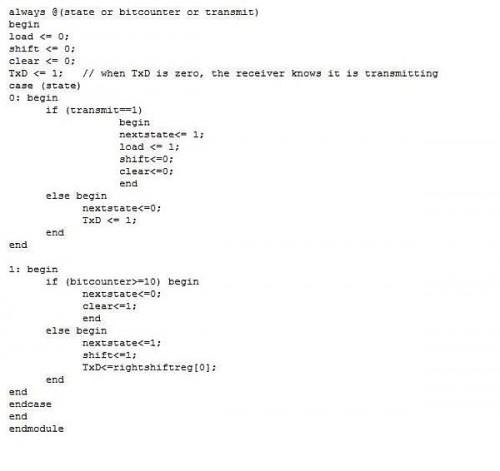

Necesitamos saber cuántos bits a la vez estamos transmitiendo, nuestro registro de desplazamiento tendrá un bit de inicio, bits de datos, bit de paridad (opcional), el bit final.Un diagrama de estado

Antes de cualquier código de escritura, hay que pensar en lo que necesitamos para crear y la mejor manera es crear un diagrama de estados de nuestro diseño. Sabemos que es un transmisor necesitamos 2 estados, y transmitir IDLE.Después de tener un diagrama de estado, ahora podemos calcular cuál será nuestro contador. Esto se hace mediante el uso de:

contador = velocidad de reloj FPGA / velocidad de transmisión

En este ejemplo utilizo una velocidad de transmisión de 9600, haciendo que mi contador = 5208.

3

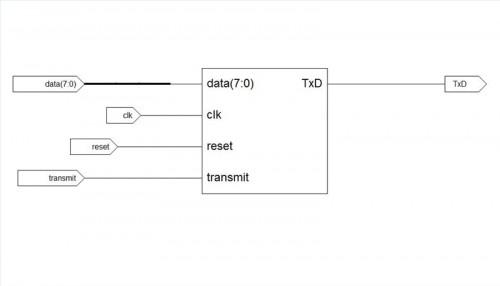

Por último, calculamos nuestro registro de desplazamiento y terminar de escribir nuestra máquina de estados. En mi código de ejemplo que utilizo un bit de inicio, bit de paridad, 8 bits de datos y bits finales. Se trata de 11 bits total.Ambas imágenes en el paso 2 y 3 juntos en el mismo módulo completo nuestro código del transmisor necesaria para programar a la FPGA. Este código funcionará con otro FPGA conectadas en serie o con HyperTerminal de Windows, entre otros equipos. Puede ser fácilmente modificable para trabajar con mucho más.

4 Por último, creamos un accesorio de prueba para corregir los errores y simular el programa antes de programar la FPGA.

Con esto concluye el transmisor. Por favor, dejar comentarios si tiene alguna pregunta o siente que hay algo que falta aquí.Consejos y advertencias

- Tanto el transmisor como el receptor deben conocer la velocidad con la que se está enviando datos.